# HFET1 SLG59H1120V

Layout Guide

#### Content

- 1. Description

- 2. Power and Ground Planes

- 3. Basic Test Setup and Connections

## **Description**

The SLG59H1120V is 18 m $\Omega$ , ~ 5 A single-channel integrated power switch that is designed to control 4.5 V to 12 V power rails. The product is packaged in an ultra-small 1.6 x 3.0 mm package.

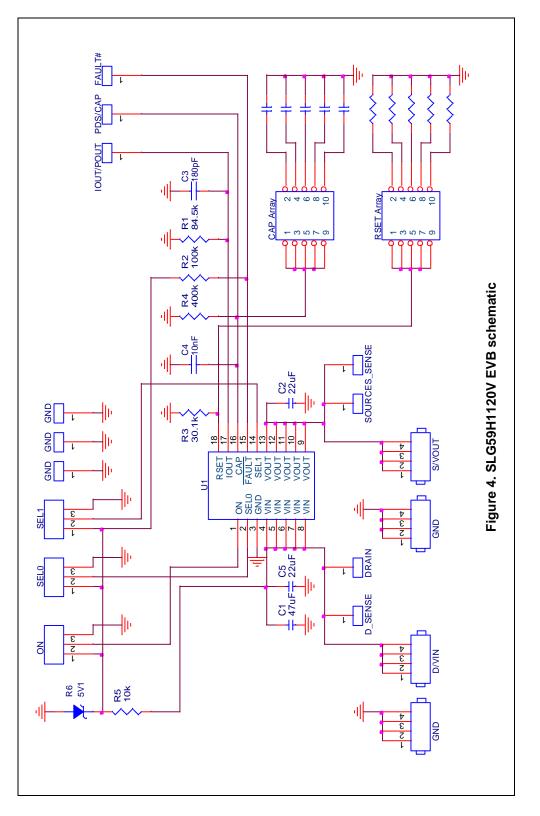

Figure 1: SLG59H1120V Block Diagram and typical application circuit for 12V operation

This layout guide provides some important information about the PCB layout of SLG59H1120V applications.

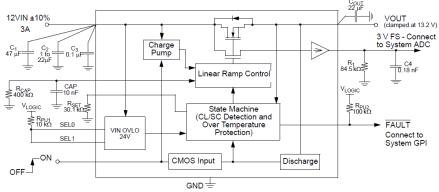

#### SILEGO STQFN 1.6 x 3 - 18L PKG

Unit: um

Figure 2. SLG59H1120V Package Dimensions and Recommended Land

Pattern

Please solder your \$LG59H1120V here

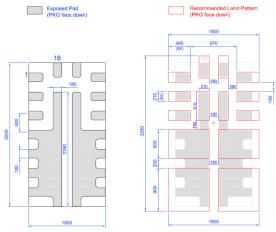

Figure 3. SLG59H1120V Evaluation Test Board

Note: Evaluation board has D\_Sense and S\_Sense pads. Please use them only for RDS(ON) evaluation.

#### 2. Power and Ground Planes

- 2.1. The trace length from the control IC to the ON, SEL0, SEL1 pins should be as short as possible and must avoid crossing this trace with power rails.

- 2.2. The VIN and VOUT pins carry significant current. Please note how the VIN and VOUT pads are placed directly on the power planes in Figure 3, which minimizes the RDS(ON) associated with long, narrow traces. The VIN and VOUT pins dissipate most of the heat generated during high-load current condition. The layout shown in Figure 3 is illustrating a proper solution for heat to transfer as efficiently as possible out of the device.

- 2.3. The GND pin (PIN3) should be connected to GND.

- 2.4. 2 oz. copper is recommended for high current operation.

- 2.5. For HFET testing, please connect as short as possible AWG14 or heavier gauge wires to VIN and VOUT terminals to avoid inductance influence on HFET during ON/OFF, Short circuit and Active Current Limit tests.

### 3. Basic Test Setup and Connections

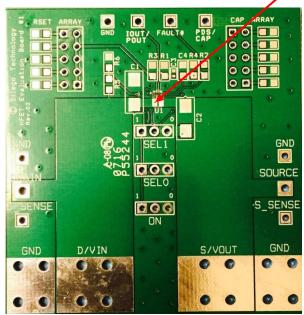

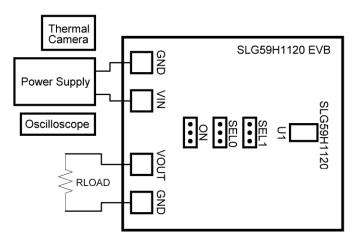

Figure 5. Typical connections for HFET Evaluation

### 3.1 Typical SEL0 and SEL1 combinations for OVLO threshold

| SEL1 | SEL0 | VIN OVLO (TYP) |

|------|------|----------------|

| 0    | 0    | 6V             |

| 0    | 1    | 10.8V          |

| 1    | 0    | 14.4V          |

| 1    | 1    | Reserved       |

# 3.2 EVB Configuration

- 1. Based on VIN voltage set SEL0, SEL1 to GND or 5V to configure OVLO

- 2. Connect oscilloscope probes to VIN, VOUT, ON, etc.

- 3. Turn ON Power Supply and set 5V, 9V or 12V

- 4. Switch ON to 5V or GND to evaluate HFET operation

Note: HFET has built-in protection to prevent over-heating. During start-up, an overly heavy load may trigger the protection feature resulting in non-monotonic VOUT ramping or repeated restarts. RLOAD must be no less than  $20\Omega$  for 12V VIN to ensure proper start-up. Once HFET is turned on, a lower RLOAD could be applied. Heavy capacitive loads with inadequate slew control can also trigger the protection circuit. Be sure to use an appropriate CSLEW to set a slow enough Slew Rate. For more information please read the Safe Start-up Condition chapter in the datasheet.