# PIC18FXX2

### PIC18FXX2 Rev. B3/B4 Silicon/Data Sheet Errata

The PIC18FXX2 Rev. B3/B4 parts you have received conform functionally to the Device Data Sheet (DS39564**B**), except for the anomalies described below.

All the issues listed here will be addressed in future revisions of the PIC18FXX2 silicon.

# The following silicon errata apply only to PIC18FXX2 devices with these Device/Revision IDs:

| Part Number | Device ID   | Revision ID |

|-------------|-------------|-------------|

| PIC18F242   | 00 0100 100 | 00101       |

| PIC18F252   | 00 0100 000 | 00101       |

| PIC18F442   | 00 0100 101 | 00101       |

| PIC18F452   | 00 0100 001 | 00101       |

The Device IDs (DEVID1 and DEVID2) are located at addresses 3FFFFEh:3FFFFh in the device's configuration space. They are shown in hexadecimal in the format "DEVID2 DEVID1".

#### 1. Module: Program Memory

Data corruption may occur during a table write operation if a peripheral interrupt also occurs. This happens only when the interrupt enable bit (PIE or INTCON register) for the corresponding interrupt has also been set.

#### Work around

Before executing any table write instructions, disable ALL peripheral interrupts. This is best done by clearing all interrupt enable bits in the three Interrupt Control registers (INTCON, INTCON2 and INTCON3) and both Peripheral Interrupt Enable registers (PIE1 and PIE2). After the table write is complete, restore all INTCON and PIE registers to their pre-instruction state.

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 2. Module: Data EEPROM

When reading the data EEPROM, the contents of the EEDATA register may become corrupted in the second instruction cycle after the RD bit (EECON1<0>) is set. The actual contents of the EEPROM remains unaffected.

#### Work around

To ensure the integrity of the contents of EEDATA, the register must be read in the instruction immediately following the setting of the RD bit. Use the MOVF or MOVFF instructions to do this (see Example 1).

Additionally, all interrupts must be disabled prior to the read instruction sequence. Interruptions of the sequence may have the same result of altering the contents of EEDATA.

#### EXAMPLE 1: SUGGESTED SEQUENCE FOR READING EEDATA

| •    |              |                                             |

|------|--------------|---------------------------------------------|

| BCF  | INTCON, GIEH | ;disable interrupts<br>;if using interrupts |

| BSF  | EECON1,RD    | ;start the read operation                   |

| MOVF | EEDATA,W     | ;move the data out of<br>;EEDATA            |

| BSF  | INTCON, GIEH | ;enable interrupts<br>;if using interrupts  |

| •    |              |                                             |

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 3. Module: Interrupts

Under certain conditions, the use of dual priority interrupts may cause a program instruction to be skipped entirely. This has only been observed when both of the following apply:

- · Both high and low interrupts are enabled, and

- A high priority asynchronous interrupt occurs in the following cycle after any low priority interrupt.

The event causes the stack to get pushed twice and will eventually result in an overflow.

#### Work around

Two possible solutions are presented. Other solutions may exist.

- 1. Enable only high priority interrupts for all sources, both synchronous and asynchronous.

- 2. If it is necessary to use both high and low interrupt priorities:

- Assign asynchronous interrupts as low priority only.

| Note: | This does not apply to the INT0 (external) |

|-------|--------------------------------------------|

|       | interrupt as it is always configured as a  |

|       | high priority interrupt.                   |

• Assign synchronous interrupts to both high and low priority, as needed.

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 4. Module: Core (Program Memory Space)

Performing table read operations above the user program memory space (addresses over 1FFFFh) may yield erroneous results at the extreme low end of the device's rated temperature range (-40°C).

This applies specifically to addresses above 1FFFFFh, including the user ID locations (20000h-200007h), the configuration bytes (300000h-30000Dh), and the device ID locations (3FFFFEh and 3FFFFFh). User program memory is unaffected.

#### Work around

Three possible work arounds are presented. Other solutions may exist.

- 1. Do not perform table read operations on areas above the user memory space at -40°C.

- Insert NOP instructions (specifically, literal FFFFh) around any table read instructions. The suggested optimal number is 4 instructions before and 8 instructions after each table read. This may vary depending upon the particular application, and should be optimized by the user.

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 5. Module: Core (Program Memory Space)

Note: This issue applies only to PIC18F252 and PIC18F452 devices with 32K words of Flash program memory. PIC18F242 and PIC18F442 devices are **not** affected.

Under certain conditions, the execution of a table read instruction may yield erroneous results. This has been observed when a table read instruction and its read destination, as indicated by the Table Pointer registers, are on opposite sides of the 4000h program memory address boundary.

This behavior has not been observed when the instruction and its target both occur strictly within the same half of the program memory space.

#### Work around

Insert a data word of value FFFFh immediately following any table read instruction. This behaves as a NOP instruction when executed. Using the actual NOP instruction instead of a literal FFFFh may not have the same results.

This is a recommended solution. Others may exist.

#### Date Codes that pertain to this issue:

All engineering samples and devices with date codes up to and including 0252 (Year 2002, Work Week 52).

#### 6. Module: Core (Program Memory Space)

Note: This issue applies only to PIC18F252 and PIC18F452 devices with 32K words of Flash program memory. PIC18F242 and PIC18F442 devices are not affected.

Under certain conditions, the execution of some control operations may yield unexpected results. This has been observed when any of the following instructions vector code execution across the 4000h program memory address boundary:

- CALL

- GOTO

- RETURN

- RETLW

- RETFIE

In addition, unexpected operation may result when an interrupt causes the device to jump across the 4000h boundary to the appropriate interrupt vector.

There are no known issues related to any of these instructions when execution occurs strictly above or below the 4000h address boundary.

#### Work around

Three possible solutions are presented. Others may exist. It is recommended to implement any one, or any combination of the three, as needed.

- Insert a data word of value FFFFh as the first instruction in the destination of a CALL or GOTO.

- 2. Insert a data word of FFFFh at the interrupt vector address(es) (0008h and/or 0018h).

- 3. Insert a data word of value FFFFh immediately following any RETURN, RETLW, or RETFIE instruction.

In each of these instances, the literal data behaves as a NOP instruction when executed. Using the actual NOP instruction instead of a literal FFFFh may not have the same results.

#### Date Codes that pertain to this issue:

All engineering samples and devices with date codes up to and including 0252 (Year 2002, Work Week 52).

#### 7. Module: Data EEPROM

When reading the data EEPROM, the contents of the EEDATA register may be corrupted if the RD bit (EECON1<0>) is set immediately following a write to the address byte (EEADR). The actual contents of the data EEPROM remain unaffected.

#### Work around

Do not set EEADR immediately before the execution of a read. Write to EEADR at least one instruction cycle before setting the RD bit. The instruction between the write to EEADR and the read can be any valid instruction including a NOP.

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 8. Module: MSSP (All I<sup>2</sup>C<sup>™</sup> and SPI<sup>™</sup> Modes)

The Buffer Full (BF) flag bit of the SSPSTAT register (SSPSTAT<0>) may be inadvertently cleared even when the SSPBUF register has not been read. This will occur only when the following two conditions occur simultaneously:

- The four Least Significant bits of the BSR register are equal to 0Fh (BSR<3:0> = 1111) and

- Any instruction that contains C9h in its 8 Least Significant bits (i.e., register file addresses, literal data, address offsets, etc.) is executed.

#### Work around

All work arounds will involve setting the contents of BSR<3:0> to some value other than 0Fh.

In addition to those proposed below, other solutions may exist.

- 1. When developing or modifying code, keep these guidelines in mind:

- Assign 12-bit addresses to all variables. This allows the assembler to know when Access Banking can be used.

- Do not set the BSR to point to Bank 15 (BSR = 0Fh).

- Allow the assembler to manipulate the access bit present in most instructions. Accessing the SFRs in Bank 15 will be done through the Access Bank. Continue to use the BSR to select all GPR Banks.

- 2. If accessing a part of Bank 15 is required and the use of Access Banking is not possible, consider using indirect addressing.

- 3. If pointing the BSR to Bank 15 is unavoidable, review the absolute file listing. Verify that no instructions contain C9h in the 8 Least Significant bits while the BSR points to Bank 15 (BSR = 0Fh).

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 9. Module: MSSP (SPI, Slave Mode)

In its current implementation, the  $\overline{SS}$  (Slave Select) control signal generated by an external master processor may not be successfully recognized by the PIC<sup>®</sup> microcontroller operating in Slave Select mode (SSPM3:SSPM0 = 0100). In particular, it has been observed that faster transitions (those with shorter fall-times) are more likely to be missed than than slower transitions.

#### Work around

Insert a series resistor between the source of the  $\overline{SS}$  signal and the corresponding  $\overline{SS}$  input line of the microcontroller. The value of the resistor is dependent on both the application system's characteristics and process variations between microcontrollers. Experimentation and thorough testing is encouraged.

This is a recommended solution. Others may exist.

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 10. Module: Core (Instruction Set)

The Decimal Adjust W register instruction, DAW, may improperly clear the Carry bit (STATUS<0>) when executed.

#### Work around

Test the Carry bit state before executing the DAW instruction. If the Carry bit is set, increment the next higher byte to be added using an instruction such as INCFSZ (this instruction does not affect any Status flags, and will not overflow a BCD nibble). After the DAW instruction has been executed, process the Carry bit normally (see Example 2).

#### EXAMPLE 2: PROCESSING THE CARRY BIT DURING BCD ADDITIONS

| MOVLW   | 0x80     | ;   | .80 (BCD)             |

|---------|----------|-----|-----------------------|

| ADDLW   | 0x80     | ;   | .80 (BCD)             |

|         |          |     |                       |

| BTFSC   | STATUS,C | ;   | test C                |

| INCFSZ  | byte2    | ;   | inc next higher LSB   |

| DAW     |          |     |                       |

| BTFSC   | STATUS,C | ;   | test C                |

| INCFSZ  | byte2    | ;   | inc next higher LSB   |

|         |          |     |                       |

| This is | repeated | for | each DAW instruction. |

|         |          |     |                       |

#### 11. Module: Timer1 Oscillator

After the system clock source for the microcontroller is switched from the primary oscillator to the Timer1 oscillator, an increase in system current consumption may occur.

#### Work around

None

#### Date Codes that pertain to this issue:

All engineering and production devices.

#### 12. Module: Reset

It has been observed that in certain Reset conditions, including power-up, the first GOTO instruction at address 0x0000 may not be executed. This occurrence is rare and affects very few applications.

To determine if your system is affected, test a statistically significant number of applications across the operating temperature, voltage and frequency ranges of the application. Affected systems will repeatably fail normal testing. Systems not affected will continue to not be affected over time.

#### Work around

Insert a NOP instruction at address 0x0000.

#### Date Codes that pertain to this issue:

All engineering and production devices.

# Clarifications/Corrections to the Data Sheet:

In the Device Data Sheet (DS39564**B**), the following clarifications and corrections should be noted.

#### 1. Module: DC Characteristics

Some of the maximum values for parameters D022A and D022B shown in **Section 22.1 "DC Characteris-tics**" of the Device Data Sheet have changed (modified text in bold):

#### 22.1 DC Characteristics: PIC18FXX2 (Industrial, Extended) PIC18LFXX2 (Industrial)

| PIC18LF      |        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |                                                                                                                                                                                         |                       |                |                                                                                |  |  |  |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|--------------------------------------------------------------------------------|--|--|--|

|              |        |                                                                                                                                    |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                       |                |                                                                                |  |  |  |

| Param<br>No. | Symbol | Characteristic                                                                                                                     | Min  | Тур                                                                                                                                                                                     | Max                   | Units          | Conditions                                                                     |  |  |  |

|              |        | Module Differential Cur                                                                                                            | rent |                                                                                                                                                                                         |                       |                |                                                                                |  |  |  |

| D022A        | ΔIBOR  | Brown-out Reset<br>PIC18LFXX2                                                                                                      |      | 29<br>29<br>33                                                                                                                                                                          | <b>40</b><br>45<br>50 | μΑ<br>μΑ<br>μΑ | VDD = 2.0V, +25°C<br>VDD = 2.0V, -40°C to +85°C<br>VDD = 4.2V, -40°C to +85°C  |  |  |  |

| D022A        |        | Brown-out Reset<br>PIC18FXX2                                                                                                       |      | 36<br>36<br>36                                                                                                                                                                          | <b>45</b><br>50<br>65 | •              | VDD = 4.2V, +25°C<br>VDD = 4.2V, -40°C to +85°C<br>VDD = 4.2V, -40°C to +125°C |  |  |  |

| D022B        | ΔILVD  | Low Voltage Detect<br>PIC18LFXX2                                                                                                   |      | 29<br>29<br>33                                                                                                                                                                          | <b>40</b><br>45<br>50 | μΑ<br>μΑ<br>μΑ | VDD = 2.0V, +25°C<br>VDD = 2.0V, -40°C to +85°C<br>VDD = 4.2V, -40°C to +85°C  |  |  |  |

| D022B        |        | Low Voltage Detect<br>PIC18FXX2                                                                                                    |      | 33<br>33<br>33                                                                                                                                                                          | <b>45</b><br>50<br>65 | μΑ<br>μΑ<br>μΑ | VDD = 4.2V, +25°C<br>VDD = 4.2V, -40°C to +85°C<br>VDD = 4.2V, -40°C to +125°C |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in hi-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR,...).

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

## 2. Module: Packaging (Pinout and Product Identification)

PIC18F442 and PICF452 devices are now offered in 44-pin, near chip-scale micro lead frame packages (commonly known as "QFN"). This packaging type has been added to the product line since the latest revision of the Device Data Sheet.

The addition of this option requires the following additions to the Device Data Sheet (DS39564B). The referenced figures and tables follow this text.

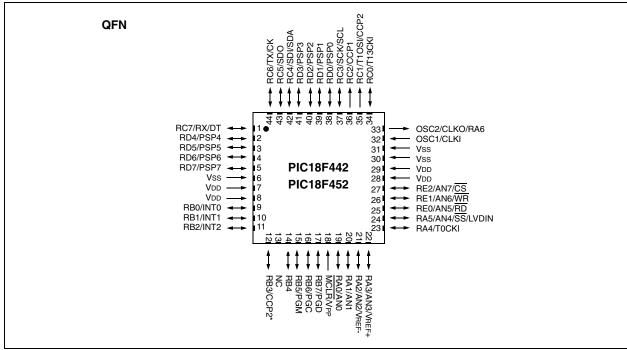

- 1. The "**Pin Diagrams**" on pages 2-3 of the Data Sheet are amended with the addition of the 44-pin QFN pinout, shown in Figure 1.

- Table 1-3 of Section 1.0 "Overview" is replaced with an updated version which adds a column for QFN pin assignments. A row is also added for previously unlisted NC pins. All new information is indicated in **bold**.

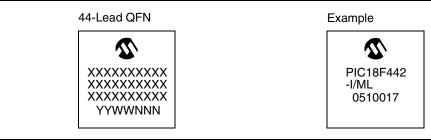

- Section 24.1 "Package Marking Information" is amended to include a marking template and example for 44-pin QFN devices. These are shown in Figure 2.

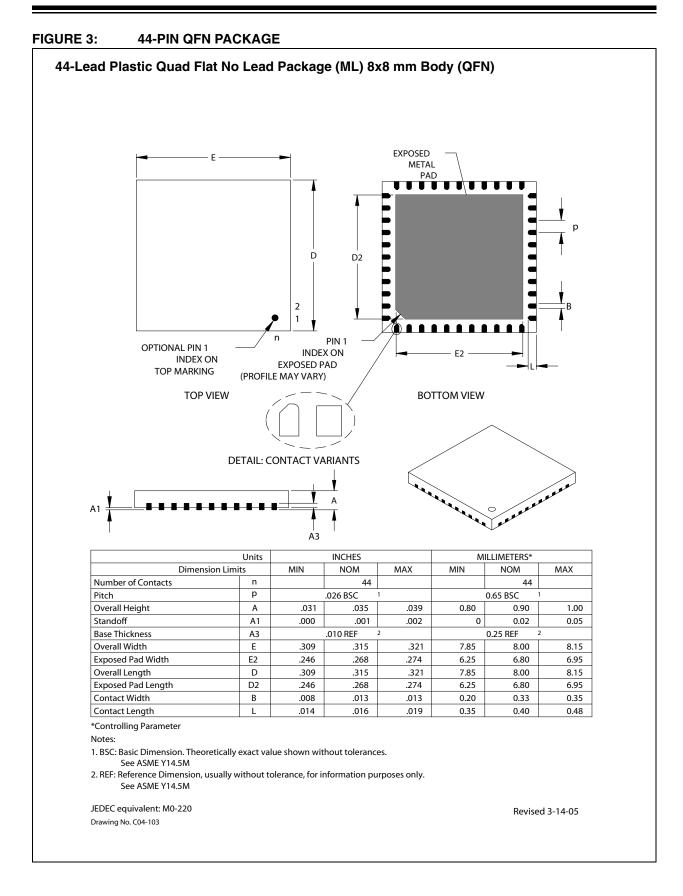

- 4. Section 24.2 (Package Details" is amended to include the mechanical drawing of the 44-pin QFN package following the existing drawings, shown in Figure 3.

- 5. In the "PIC18F442/452 Product Identification System" (page 329), the "Package" options are amended to include the new line item:

ML = QFN

For the sake of completeness, it is also noted that the package designation "MLF" is now replaced by "QFN" in all occurrences throughout the Device Data Sheet. "MLF" should be considered an obsoleted term.

#### FIGURE 1: PINOUT DIAGRAM FOR PIC18F442/452, 44-PIN QFN PACKAGE

#### FIGURE 2: PACKAGE MARKING TEMPLATE FOR PIC18F442/452, 44-PIN QFN

| Pin Name                                      | DIP |      | Pin Number |      | Pin Buffer        | Deserintion                   |                                                                                                                                                                     |

|-----------------------------------------------|-----|------|------------|------|-------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLB/VPP                                      |     | PLCC | QFN        | TQFP | Туре              | Туре                          | Description                                                                                                                                                         |

| MCLR                                          | 1   | 2    | 18         | 18   | I                 | ST                            | Master Clear (input) or high voltage ICSP™<br>programming enable pin.<br>Master Clear (Reset) input. This pin is an active<br>low Reset to the device.              |

| Vpp                                           |     |      |            |      | Ι                 | ST                            | High-Voltage ICSP programming enable pin.                                                                                                                           |

| NC                                            | —   |      | 32         |      | —                 |                               | These pins should be left unconnected.                                                                                                                              |

| OSC1/CLKI<br>OSC1                             | 13  | 14   | 33         | 30   | I                 | ST                            | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode,<br>CMOS otherwise. |

| CLKI                                          |     |      |            |      | -                 | CMOS                          | External clock source input. Always associated<br>with pin function OSC1. (See related<br>OSC1/CLKI, OSC2/CLKO pins.)                                               |

| OSC2/CLKO/RA6<br>OSC2                         | 14  | 15   |            | 31   | 0                 | _                             | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal                                                                               |

| CLKO                                          |     |      |            |      | 0                 | —                             | or resonator in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.    |

| RA6                                           |     |      |            |      | I/O               | TTL                           | General Purpose I/O pin.                                                                                                                                            |

|                                               |     |      |            |      |                   |                               | PORTA is a bidirectional I/O port.                                                                                                                                  |

| RA0/AN0<br>RA0<br>AN0                         | 2   | 3    | 19         | 19   | I/O<br>I          | TTL<br>Analog                 | Digital I/O.<br>Analog input 0.                                                                                                                                     |

| RA1/AN1<br>RA1<br>AN1                         | 3   | 4    | 20         | 20   | I/O<br>I          | TTL<br>Analog                 | Digital I/O.<br>Analog input 1.                                                                                                                                     |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF-          | 4   | 5    | 21         | 21   | I/O<br>I<br>I     | TTL<br>Analog<br>Analog       | Digital I/O.<br>Analog input 2.<br>A/D Reference Voltage (Low) input.                                                                                               |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+          | 5   | 6    | 22         | 22   | I/O<br>I<br>I     | TTL<br>Analog<br>Analog       | Digital I/O.<br>Analog input 3.<br>A/D Reference Voltage (High) input.                                                                                              |

| RA4/T0CKI<br>RA4<br>T0CKI                     | 6   | 7    | 23         | 23   | I/O<br>I          | ST/OD<br>ST                   | Digital I/O. Open-drain when configured as output.<br>Timer0 external clock input.                                                                                  |

| RA5/AN4/SS/LVDIN<br>RA5<br>AN4<br>SS<br>LVDIN | 7   | 8    | 24         | 24   | I/O<br> <br> <br> | TTL<br>Analog<br>ST<br>Analog | Digital I/O.<br>Analog input 4.<br>SPI™ Slave Select input.<br>Low-Voltage Detect input.                                                                            |

| RA6                                           |     |      |            |      |                   |                               | (See the OSC2/CLKO/RA6 pin.)                                                                                                                                        |

TABLE 1-3: PIC18F4X2 PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels

ΠÞ I = Input

O = Output OD = Open Drain (no P diode to VDD) P = Power

| Pin Name                |           | Pin N    | umber    |      | Pin        | Buffer                                 | Description                                                                                                   |

|-------------------------|-----------|----------|----------|------|------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------|

|                         | DIP       | PLCC     | QFN      | TQFP | Туре       | Туре                                   | Description                                                                                                   |

|                         |           |          |          |      |            |                                        | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0<br>RB0<br>INT0 | 33        | 36       | 9        | 8    | I/O<br>I   | TTL<br>ST                              | Digital I/O.<br>External Interrupt 0.                                                                         |

| RB1/INT1<br>RB1<br>INT1 | 34        | 37       | 10       | 9    | I/O<br>I   | TTL<br>ST                              | Digital I/O.<br>External Interrupt 1.                                                                         |

| RB2/INT2<br>RB2<br>INT2 | 35        | 38       | 11       | 10   | I/O<br>I   | TTL<br>ST                              | Digital I/O.<br>External Interrupt 2.                                                                         |

| RB3/CCP2<br>RB3<br>CCP2 | 36        | 39       | 12       | 11   | I/O<br>I/O | TTL<br>ST                              | Digital I/O.<br>Capture2 input, Compare2 output, PWM2 output.                                                 |

| RB4                     | 37        | 41       | 14       | 14   | I/O        | TTL                                    | Digital I/O. Interrupt-on-change pin.                                                                         |

| RB5/PGM<br>RB5<br>PGM   | 38        | 42       | 15       | 15   | I/O<br>I/O | TTL<br>ST                              | Digital I/O. Interrupt-on-change pin.<br>Low-Voltage ICSP™ programming enable pin.                            |

| RB6/PGC<br>RB6<br>PGC   | 39        | 43       | 16       | 16   | I/O<br>I/O | TTL<br>ST                              | Digital I/O. Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.                  |

| RB7/PGD<br>RB7<br>PGD   | 40        | 44       | 17       | 17   | I/O<br>I/O | TTL<br>ST                              | Digital I/O. Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data<br>pin.                |

| Legend: TTL = TTL       | •         | •        |          |      |            | CMOS = CMOS compatible input or output |                                                                                                               |

| ST = Schm               | in i rigg | jer inpu | t with C |      | eveis      |                                        | I = Input                                                                                                     |

#### PIC18F4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

O = Output OD = Open Drain (no P diode to VDD)

P = Power

| TABLE 1-3: | PIC18F4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------------|

|------------|-----------------------------------------------|

| Din Nome                                          | Pin Number |      |     | Pin  | Pin Buffer        | Description      |                                                                                                                                         |

|---------------------------------------------------|------------|------|-----|------|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                          | DIP        | PLCC | QFN | TQFP | Туре              | Туре             | Description                                                                                                                             |

|                                                   |            |      |     |      |                   |                  | PORTC is a bidirectional I/O port.                                                                                                      |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI          | 15         | 16   | 34  | 32   | I/O<br>O<br>I     | ST<br>—<br>ST    | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                        |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2            | 16         | 18   | 35  | 35   | I/O<br>I<br>I/O   | ST<br>CMOS<br>ST | Digital I/O.<br>Timer1 oscillator input.<br>Capture2 input, Compare2 output,<br>PWM2 output.                                            |

| RC2/CCP1<br>RC2<br>CCP1                           | 17         | 19   | 36  | 36   | I/O<br>I/O        | ST<br>ST         | Digital I/O.<br>Capture1 input/Compare1 output/<br>PWM1 output.                                                                         |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                  | 18         | 20   | 37  | 37   | I/O<br>I/O<br>I/O | ST<br>ST<br>ST   | Digital I/O.<br>Synchronous serial clock input/output for<br>SPI™ mode.<br>Synchronous serial clock input/output for                    |

| 301                                               |            |      |     |      | 1/0               | 51               | $I^2C^{TM}$ mode.                                                                                                                       |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                  | 23         | 25   | 42  | 42   | I/O<br>I<br>I/O   | ST<br>ST<br>ST   | Digital I/O.<br>SPI Data In.<br>I <sup>2</sup> C Data I/O.                                                                              |

| RC5/SDO<br>RC5<br>SDO                             | 24         | 26   | 43  | 43   | I/O<br>O          | ST<br>—          | Digital I/O.<br>SPI Data Out.                                                                                                           |

| RC6/TX/CK<br>RC6<br>TX<br>CK                      | 25         | 27   | 44  | 44   | I/O<br>O<br>I/O   | ST<br>—<br>ST    | Digital I/O.<br>USART Asynchronous Transmit.<br>USART Synchronous Clock<br>(see related RX/DT).                                         |

| RC7/RX/DT<br>RC7<br>RX<br>DT<br>Legend: TTL = TTL | 26         | 29   | 1   | 1    | I/O<br>I<br>I/O   | ST<br>ST<br>ST   | Digital I/O.<br>USART Asynchronous Receive.<br>USART Synchronous Data<br>(see related TX/CK).<br>CMOS = CMOS compatible input or output |

Legend: TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

O = Output

OD = Open Drain (no P diode to VDD)

$\label{eq:cmost} \begin{array}{l} \mathsf{CMOS} = \mathsf{CMOS} \text{ compatible input or output} \\ \mathsf{I} = \mathsf{Input} \\ \mathsf{P} = \mathsf{Power} \end{array}$

| TABLE 1-3: | PIC18F4X2 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-----------------------------------------------|

|------------|-----------------------------------------------|

| <b>cc</b><br>21<br>22<br>23<br>24<br>30 | QFN<br>38<br>39<br>40 | <b>TQFP</b><br>38<br>39              | Type<br>I/O                                                                    | <b>Type</b><br>ST                                     | Description<br>PORTD is a bidirectional I/O port, or a Parallel Slav<br>Port (PSP) for interfacing to a microprocessor port<br>These pins have TTL input buffers when PSP |

|-----------------------------------------|-----------------------|--------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22<br>23<br>24                          | 39                    |                                      | I/O                                                                            | ST                                                    | Port (PSP) for interfacing to a microprocessor port<br>These pins have TTL input buffers when PSP                                                                         |

| 22<br>23<br>24                          | 39                    |                                      | I/O                                                                            | ST                                                    | module is enabled.                                                                                                                                                        |

| 23<br>24                                |                       | 39                                   |                                                                                | TTL                                                   | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

| 24                                      | 40                    |                                      | I/O                                                                            | ST<br>TTL                                             | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

|                                         |                       | 40                                   | I/O                                                                            | ST<br>TTL                                             | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

| 30                                      | 41                    | 41                                   | I/O                                                                            | ST<br>TTL                                             | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

| -                                       | 2                     | 2                                    | I/O                                                                            | ST<br>TTL                                             | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

| 31                                      | 3                     | 3                                    | I/O                                                                            | ST<br>TTL                                             | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

| 32                                      | 4                     | 4                                    | I/O                                                                            | ST<br>TTL                                             | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

| 33                                      | 5                     | 5                                    | I/O                                                                            | ST<br>TTL                                             | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                 |

| 9                                       | 25                    | 25                                   | I/O                                                                            | ST<br>TTL                                             | PORTE is a bidirectional I/O port.<br>Digital I/O.<br>Read cont <u>rol f</u> or pa <u>ral</u> lel slave port                                                              |

| 0                                       | 26                    | 26                                   | I/O                                                                            | Analog<br>ST                                          | (see also WR and CS pins).<br>Analog input 5.<br>Digital I/O.                                                                                                             |

|                                         |                       |                                      |                                                                                | TTL                                                   | Write control for parallel slave port (see $\overline{CS}$ and $\overline{RD}$ pins).                                                                                     |

| 1                                       | 27                    | 27                                   | I/O                                                                            | Analog<br>ST<br>TTL                                   | Analog input 6.<br>Digital I/O.<br>Chip Select control for parallel slave port                                                                                            |

|                                         |                       |                                      |                                                                                | Analog                                                | (see related RD and WR).<br>Analog input 7.                                                                                                                               |

| , 34                                    | 6, 30,<br>31          | 6, 29                                | Ρ                                                                              | _                                                     | Ground reference for logic and I/O pins.                                                                                                                                  |

| , 35                                    |                       | 7, 28                                | Ρ                                                                              |                                                       | Positive supply for logic and I/O pins.                                                                                                                                   |

| 17,                                     | 13                    | 12, 13,<br>33, 34                    | —                                                                              | _                                                     | These pins are not internally connected. They should be left unconnected.                                                                                                 |

| ,                                       | 35<br>7,<br>1         | 35 7, 8,<br>28, 29<br>7, 13<br>input | 31       35     7, 8, 28, 29       7, 13     12, 13, 33, 34       input     35 | 31   35 7, 8, 7, 28   28, 29   7, 13 12, 13,   33, 34 | 34   6, 30, 6, 29   P   —     31   31   —   —     35   7, 8, 7, 28   P   —     28, 29   —   —   —     7, 13   12, 13, —   —   —     39   —   33, 34   —   —               |

OD = Open Drain (no P diode to VDD)

DS80127G-page 10

#### **REVISION HISTORY**

#### Rev A Document (4/2002)

First revision of this document, silicon issues 1 (Program Memory) and 2 (Data EEPROM) and data sheet issues 1 (Interrupts), 2 and 3 (USART) and 4 (Program Memory).

#### Rev B Document (7/2002)

Added silicon issues 3 and 4 (Interrupts and Core - Program Memory Space).

#### Rev C Document (10/2002)

All data sheet issues were removed. Added silicon issues 5, 6 and 7 (Core - Program Memory Space and Data EEPROM).

#### Rev D Document (1/2003)

Updated date code information for silicon issues 5 and 6 (Core - Program Memory Space), and added data sheet issue 1 (DC Characteristics). Rev. B4 Silicon was included along with Rev. B3 Silicon in this document revision.

#### Rev E Document (3/2003)

Updated silicon issue 6 (Core - Program Memory Space). Added silicon issues 8, 9 and 10 (MSSP and Core - Instruction Set) and data sheet clarification 2 (Packaging - Pinout and Product Identification).

Rev F Document (7/2003)

Added silicon issue 11 (Timer1 Oscillator).

Rev G Document (05/2005)

Added silicon issue 12 (Reset).

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance and WiperLock are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2005, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

**San Jose** Mountain View, CA Tel: 650-215-1444 Fax: 650-961-0286

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8676-6200 Fax: 86-28-8676-6599

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

China - Hong Kong SAR Tel: 852-2401-1200 Fax: 852-2401-3431

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066 China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Shunde** Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Qingdao** Tel: 86-532-502-7355 Fax: 86-532-502-7205

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-2229-0061 Fax: 91-80-2229-0062

India - New Delhi Tel: 91-11-5160-8631 Fax: 91-11-5160-8632

**Japan - Kanagawa** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel:011-604-646-8870 Fax:011-604-646-5086

Philippines - Manila Tel: 011-632-634-9065 Fax: 011-632-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Taiwan - Hsinchu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

#### EUROPE

Austria - Weis Tel: 43-7242-2244-399 Fax: 43-7242-2244-393

**Denmark - Ballerup** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Massy Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Ismaning** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

England - Berkshire Tel: 44-118-921-5869 Fax: 44-118-921-5820